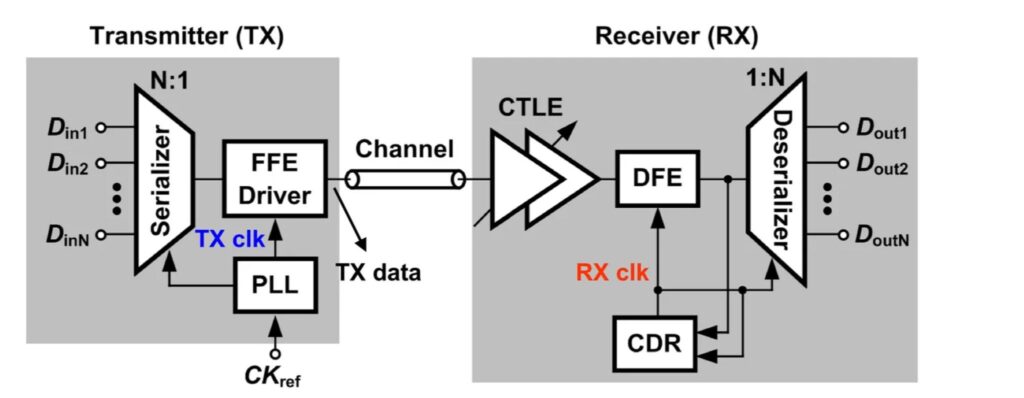

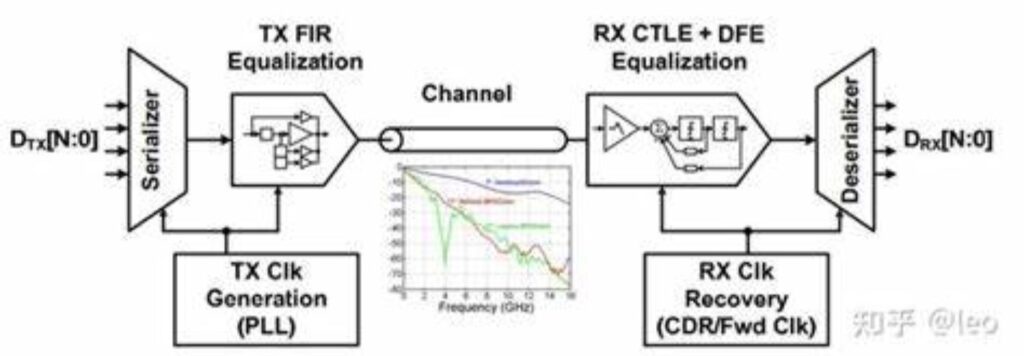

Overview of CTLE & DFE in SERDES RX Architecture

CTLE (Continuous-Time Linear Equalizer)

CTLE is a key component in the RX (Receiver) architecture of SERDES (Serializer/Deserializer) systems, primarily designed to compensate for frequency-dependent losses that occur during high-speed signal transmission. Its main purpose is to target high-frequency components of the signal that may be attenuated, thereby improving overall signal quality.

How CTLE Works

CTLE operates by adjusting the frequency response of incoming signals, boosting certain frequency ranges while attenuating others. This process is crucial for maintaining the integrity of transmitted data. Unlike discrete-time equalizers, CTLE processes signals in continuous time, allowing for effective equalization of high-speed signals without introducing additional delay.

Advs & Limitations

One significant advantage of CTLE is its low latency; operating in the continuous domain allows it to introduce minimal delay, making it ideal for high-speed applications. Additionally, its relatively simple architecture facilitates compact designs. However, CTLE has limitations, as it may not sufficiently correct severe inter-symbol interference (ISI) caused by reflections and other nonlinear effects.

DFE (Decision Feedback Equalizer)

DFE is another critical component in RX SERDES systems, aimed at reducing inter-symbol interference by leveraging previously made decisions about transmitted symbols to enhance current symbol detection. This function is particularly beneficial in high-speed data communications where signal overlap occurs.

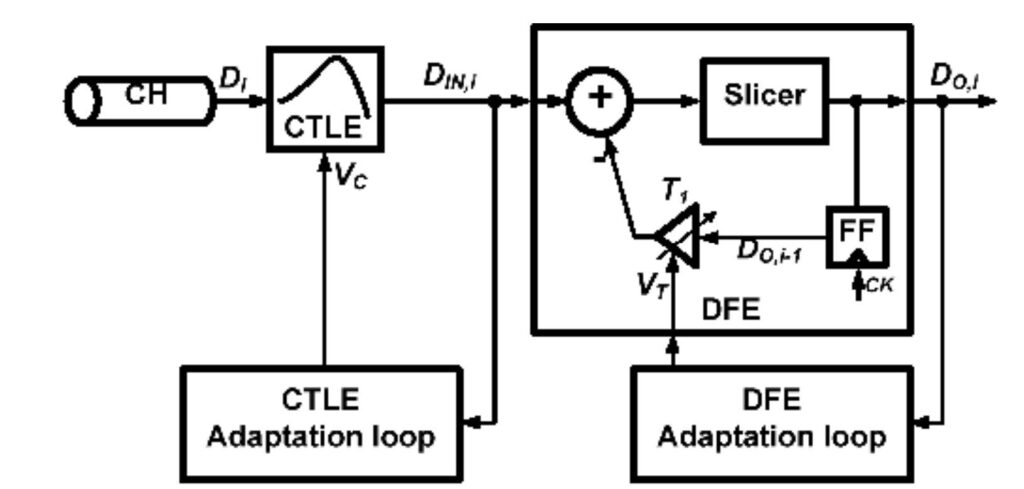

How DFE Works

The DFE operates through a feedback mechanism, where it subtracts the estimated contribution of previous symbols from the current input signal. It consists of two main components: a feedforward filter, which processes the incoming signal to provide an initial estimate of the current symbol, and a feedback filter, which takes previously decided symbols and subtracts their contributions to mitigate ISI.

Adv & Limitations

DFE is particularly effective at mitigating ISI, significantly improving symbol detection accuracy in environments where ISI is prevalent, especially at higher data rates. Its adaptive nature allows it to adjust to varying channel conditions, providing robust performance. However the feedback mechanism can introduce increased latency, which may be a concern in ultra-low-latency applications. Additionally, the complexity of DFE can lead to higher power consumption and design challenges.

Conclusion

In modern RX SERDES architectures, both CTLE and DFE play complementary roles in enhancing signal integrity. CTLE focuses on correcting frequency losses, while DFE addresses inter-symbol interference. Together, these components are essential for achieving high-performance data transmission and enabling reliable high-speed communication.