SERDES: The Architecture Behind High-Speed Data Conversion

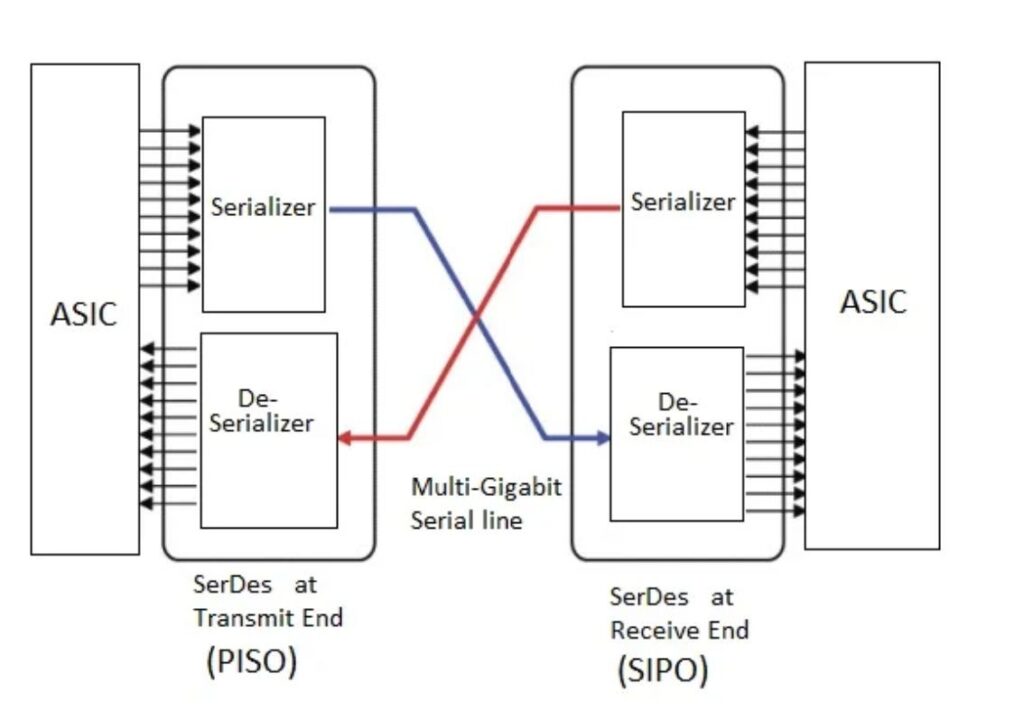

SERDES, which stands for Serializer/Deserializer, is a key technology used in high-speed data communication systems to manage data conversion between parallel and serial formats. It is integral to reducing the number of data lines required and enabling faster data transmission.

The serializer in a SERDES system is responsible for converting parallel data into a serial stream. It achieves this by aligning and multiplexing multiple parallel data lines into a single high-speed serial format. This process often includes clock data recovery (CDR) to extract timing information from the serial stream, ensuring that data is aligned and timed correctly. Additionally, some serializers use encoding techniques, such as 8b/10b encoding, to maintain data integrity and manage the DC balance in the serial data stream.

On the other hand, the deserializer converts the received serial data back into parallel form. This involves demultiplexing the serial data into multiple parallel lines, a process that also relies on clock recovery to synchronize with the incoming data stream. The deserializer may also include decoding mechanisms to interpret encoded data correctly.

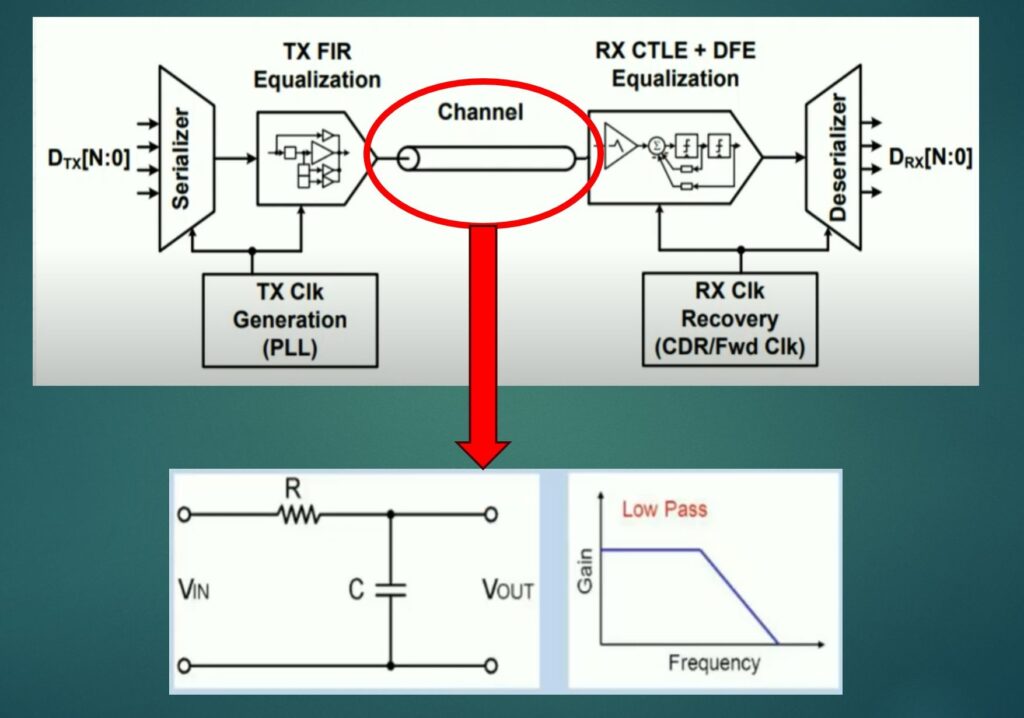

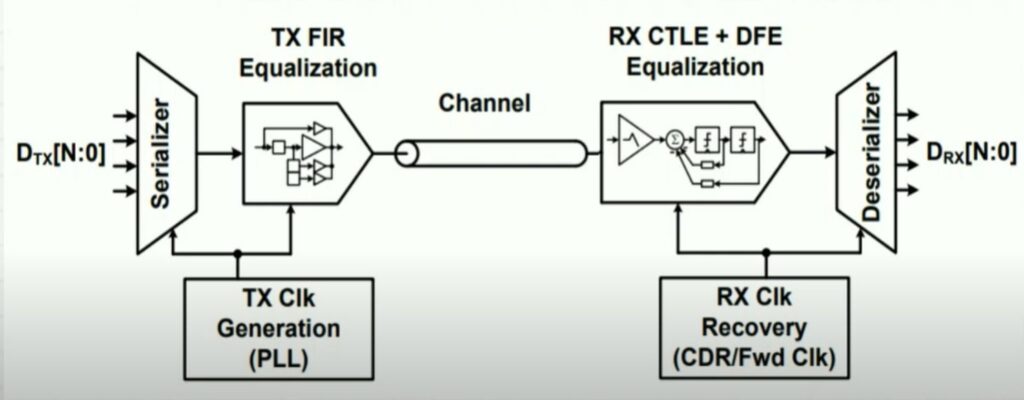

In a SERDES system, the transmitter section of the serializer modulates and transmits the serial data over the communication medium, often using differential signaling to improve signal integrity and reduce noise. Conversely, the receiver section of the deserializer demodulates and processes the incoming serial data, typically incorporating equalization techniques to address signal degradation.

Clocking is crucial in SERDES architecture, as it provides the necessary signals for both serialization and deserialization processes. This includes generating and distributing clock signals to align and time the data accurately. Additionally, equalization techniques are employed to compensate for signal loss and distortion, which is particularly important in high-speed transmissions.

Error detection and correction mechanisms are also essential in SERDES systems to ensure data integrity. These mechanisms often include error-checking codes and retry protocols to handle any errors that occur during data transmission.

SERDES technology is widely applied in high-speed communication interfaces such as Ethernet, PCIe, and SATA, as well as in data storage systems, networking equipment, and consumer electronics like HDMI and DisplayPort. Its role in enabling efficient and high-speed data transfers makes it a cornerstone of modern electronic systems and communications.