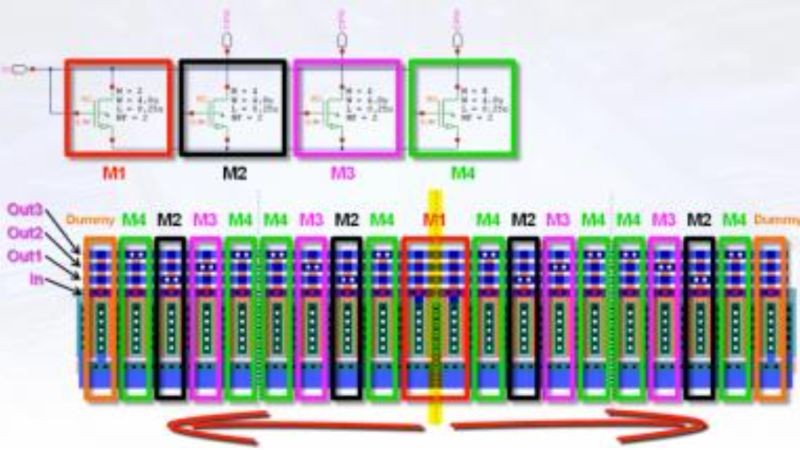

Leakage Mechanisms in Half Dummy vs Full Dummy Analog Layout Designs

Full_Dummy:

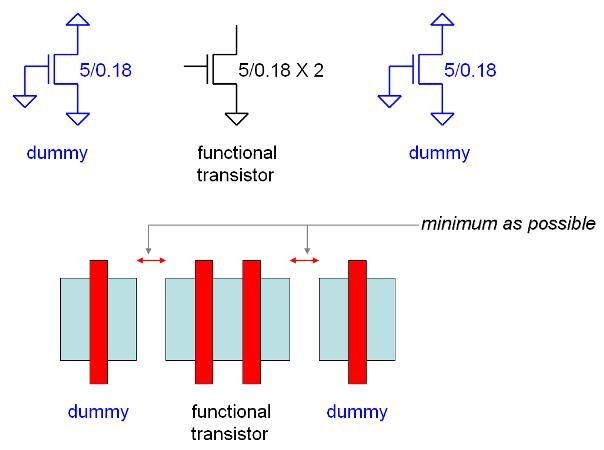

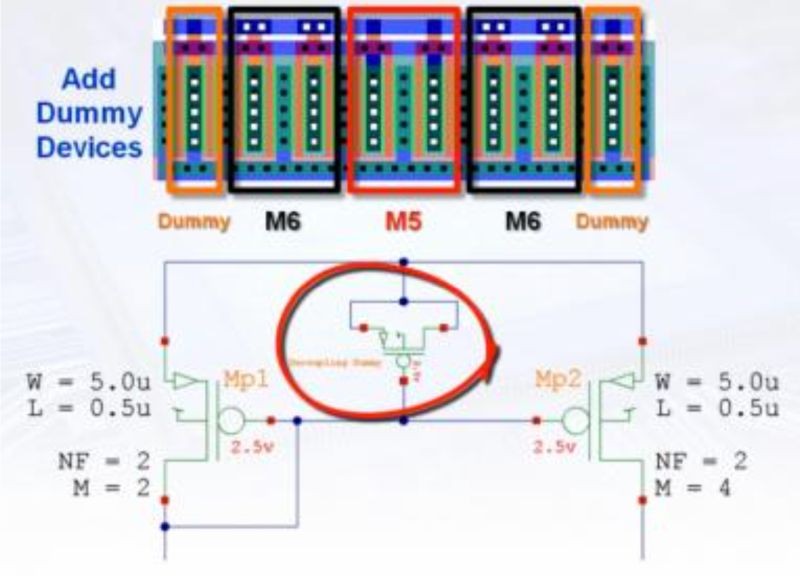

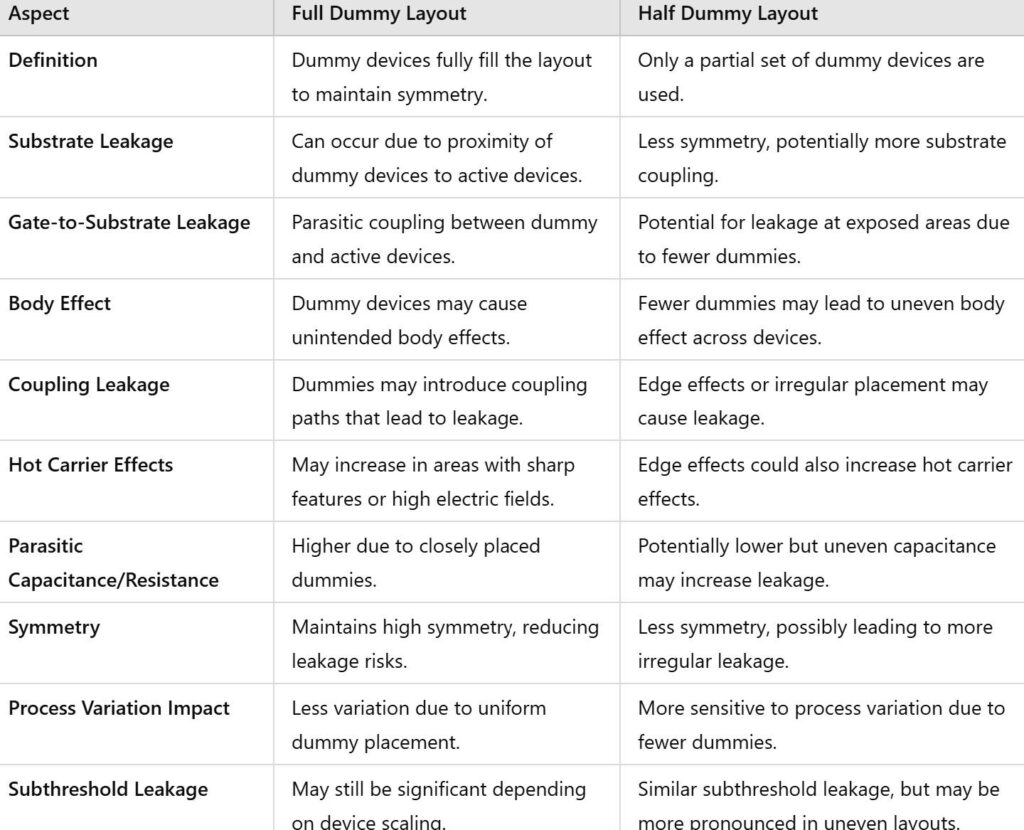

Definition: In full dummy layout, dummy devices (non-functional devices) are inserted in the layout to maintain symmetry, improve design robustness, and manage parasitic capacitance. These dummy devices are usually added to fill the space and prevent issues like hot carrier injection and random dopant fluctuation.

Leakage_Mechanisms: Substrate Leakage: Even though the dummy devices are non-functional, they may still experience leakage due to substrate connections, especially if the distance between them and active devices is small enough to cause unintended coupling or capacitive effects.

Gate-to-Substrate Leakage: Parasitic gate-to-substrate or gate-to-drain coupling may cause leakage currents, especially in the case of thin-oxide transistors or when the dummy devices are improperly placed.

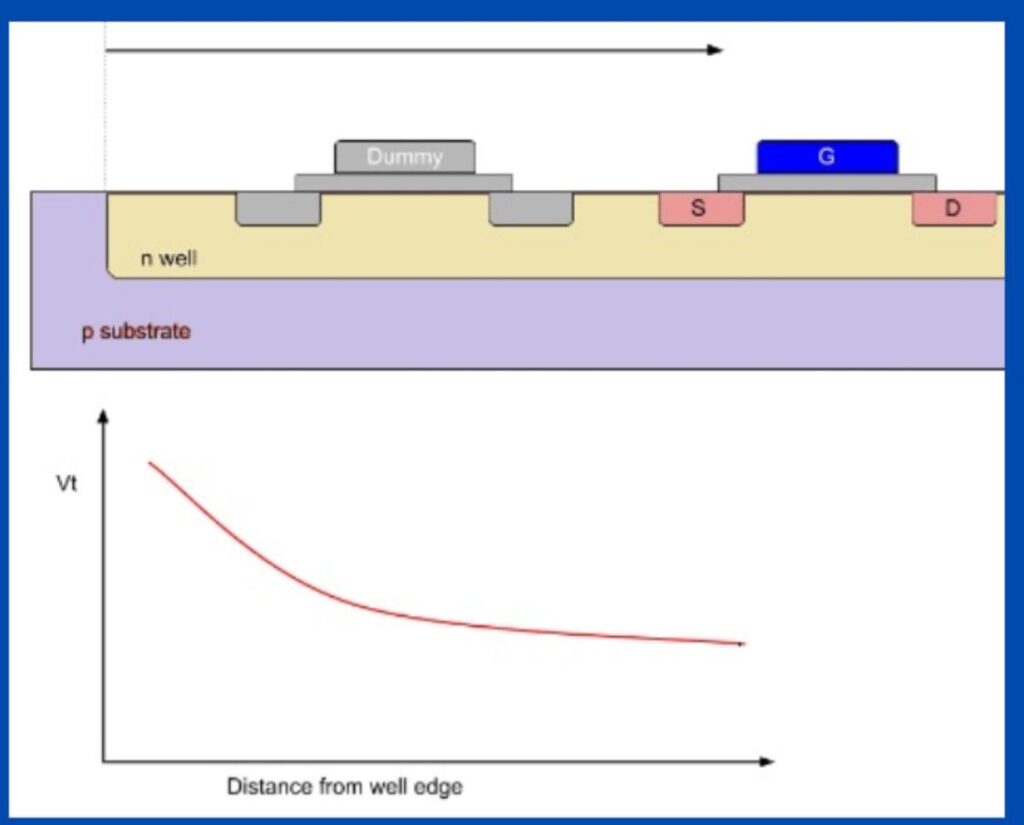

Body_Effect: Dummy devices, if connected to the wrong substrate potential, may cause body effect on surrounding active devices, influencing their threshold voltage and increasing leakage currents.

Coupling_Leakage: In some cases, dummies may create coupling paths that allow leakage current to flow, especially when there’s a voltage difference between them and the active devices.

Half_Dummy:

Definition: In half dummy layout, only a partial set of dummy devices is used, typically on one side or a limited part of the design. This approach is less aggressive than full dummy layouts and is often used to save area and reduce parasitic effects.

Leakage_Mechanisms: Reduced Symmetry: With fewer dummy devices, there might be less uniformity in the layout, which can lead to greater leakage due to irregularities in the parasitic elements.

Substrate_Coupling: The absence of dummies in certain areas can cause uneven substrate coupling between active devices, leading to localized leakage paths.

Hot_Carrier_Effects: Half dummy layout has sharp features or regions where electric fields are high, hot carrier injection could occur, leading to leakage.

General Leakage Factors in Both Layout Techniques:

Parasitic: Regardless of full or half dummies, the layout will have parasitic capacitance between interconnects and the substrate, which may contribute to leakage.

Subthreshold_Leakage: As technology scales down, subthreshold leakage becomes more significant, and both full and half dummy layouts.

Gate_Leakage: With scaling, gate leakage may become more prominent. Improper placement of dummy devices can increase the proximity of gates, leading to higher gate leakage.

Summary:

Full Dummy Layout may have leakage due to unintended coupling, body effects, or interactions between the dummy devices and active devices, though the impact is typically minimized by their design intent.

Half Dummy Layout can have more pronounced leakage risks due to less symmetry, increased edge effects, and more irregular coupling between devices.