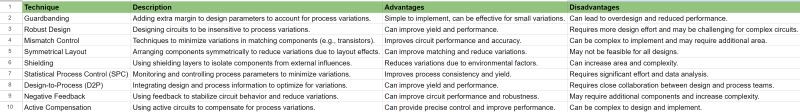

Strategies for mitigating process variations in circuit design and layout

Design_Strategies

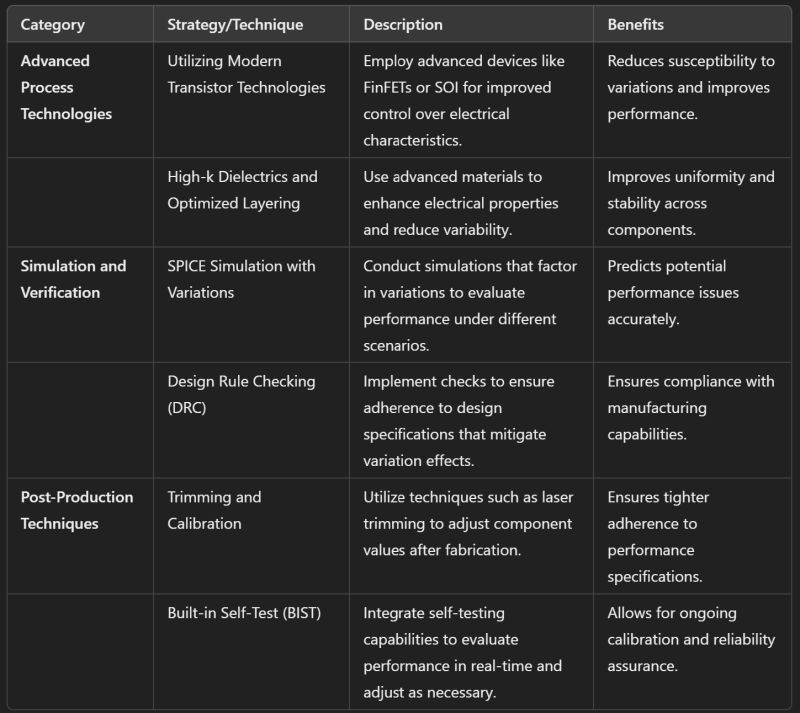

Statistical Design Techniques:

– Monte Carlo Simulations: Use these to assess the statistical impact of variations on circuit performance. By simulating a large number of scenarios, designers can understand how variations influence key metrics.

– Design for Manufacturability (DFM): This approach involves designing circuits that are easier and more reliable to manufacture. Techniques include ensuring sufficient space for fabrication processes and avoiding complex geometries that might lead to increased variability.

Adaptive Circuits:

– Self-Calibrating Circuits: Incorporate mechanisms that allow circuits to adjust parameters dynamically in response to real-time performance measurements. For example, using on-chip reference circuits that can adjust bias currents based on detected output variations.

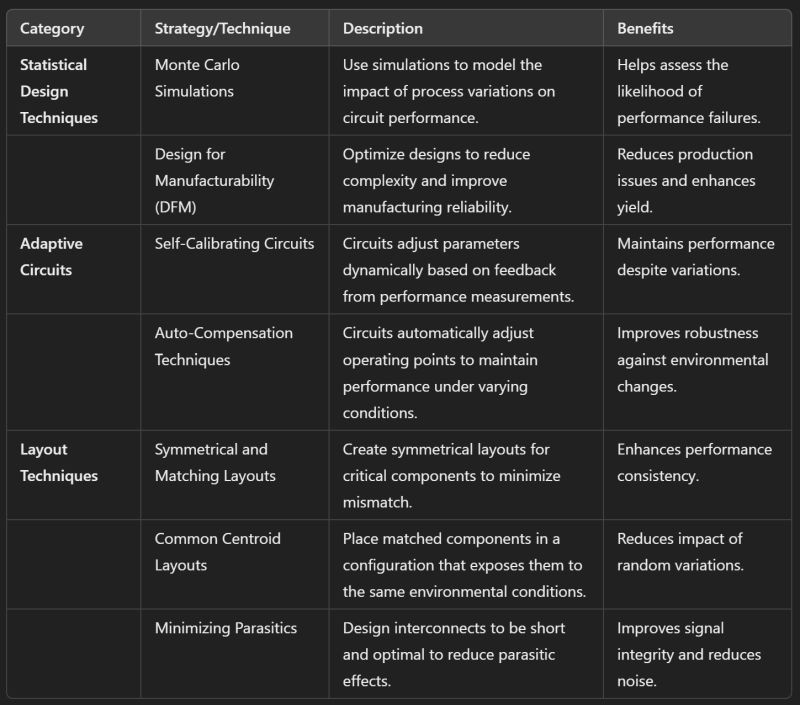

Layout_Techniques

Symmetrical and Matching Layouts:

– Symmetrical Designs: Create symmetrical layouts for critical components, which helps balance out variations across the circuit. This is especially useful in differential circuits, where matching performance is crucial.

– Common Centroid Layouts: Use this technique for matched pairs of transistors or resistors to ensure that any variation affects both devices equally, thereby canceling out the effects of mismatch.

Minimizing Parasitics:

– Short Interconnects: Design interconnects to be as short as possible to reduce parasitic capacitance and inductance, which can exacerbate variations in signal integrity.

– Optimal Routing Strategies: Implement routing practices that minimize cross-talk and noise coupling, ensuring stable operation despite variations.

Simulation_and_Verification

SPICE Simulation with Variations:

– Conduct detailed SPICE simulations that incorporate process variations to evaluate the impact on circuit performance across different operating conditions and scenarios.

Design Rule Checking (DRC):

– Implement rigorous design rule checks to ensure the layout adheres to specifications that minimize the effects of process variations. This includes verifying minimum feature sizes, spacing, and alignment tolerances.

Built-in Self-Test (BIST):

– Integrate BIST capabilities into designs to allow for real-time performance evaluation and calibration. This can help identify variations during operation and adjust accordingly.

Conclusion

By combining robust design strategies, careful layout considerations, advanced technologies, and thorough testing and calibration methods, designers can effectively mitigate the impacts of process variations. This comprehensive approach enhances the reliability and performance of analog circuits, ensuring they meet specifications in a manufacturing environment characterized by inevitable variations.