Static Timing Analysis (STA) flow

Overview of the STA Flow:

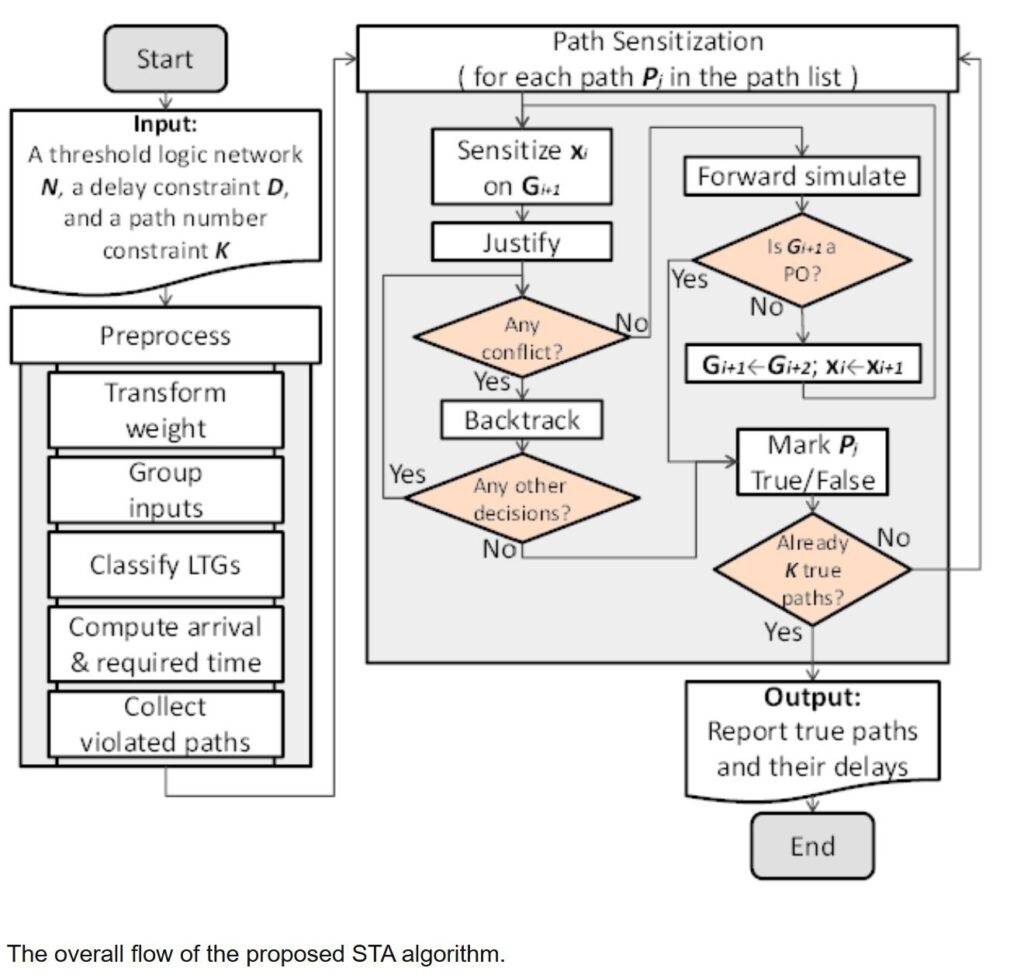

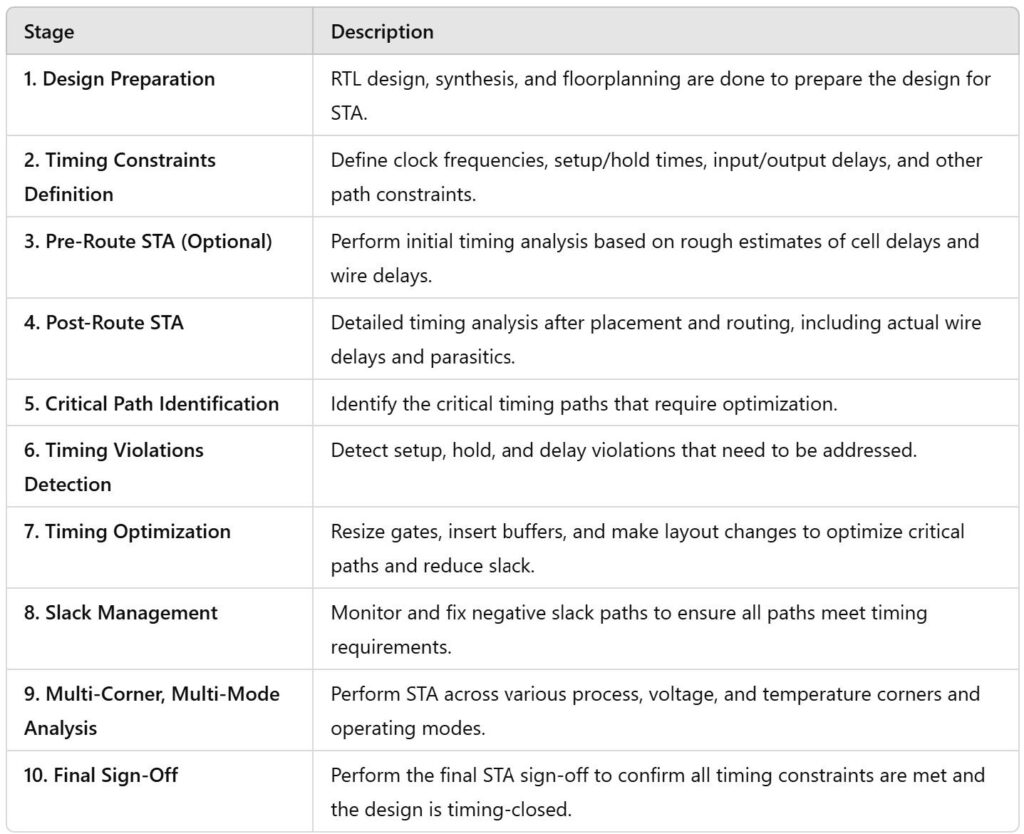

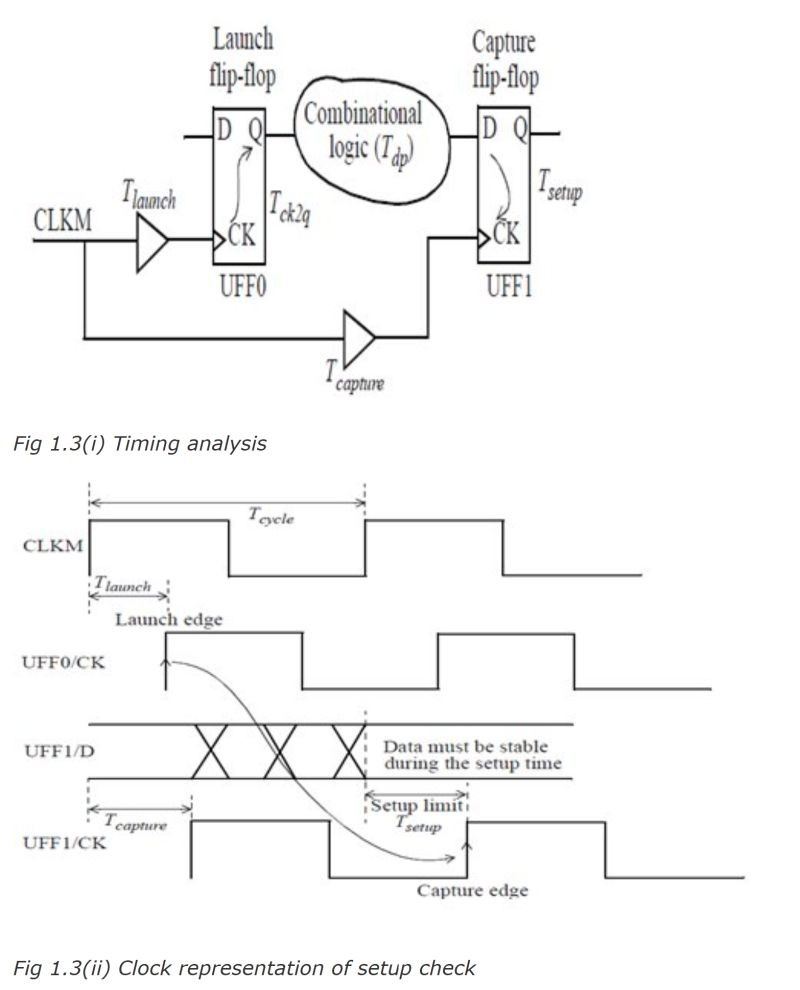

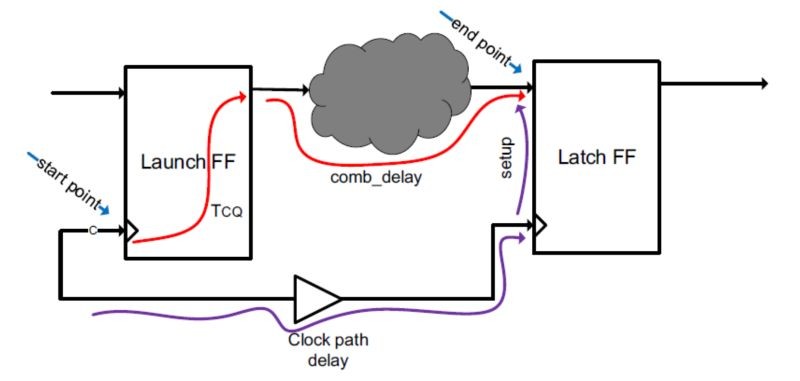

Static Timing Analysis (STA) is an essential process in the physical design flow, where timing constraints are checked to ensure that signals propagate correctly through the circuit. STA doesn’t require dynamic simulation but instead uses timing models to check if the design satisfies setup, hold, and other timing requirements. STA Flow in detail,

Design_Preparation:

RTL Design: Start with the RTL design, where timing constraints are set for clocks, setup/hold times, input/output delays, and other path-related constraints.

Synthesis: After RTL synthesis, the design is converted into a gate-level netlist. Here, logic gates and flip-flops replace high-level RTL descriptions.

Floorplanning: Placement and partitioning of blocks are done for efficient routing, which affects timing.

Clock Tree Synthesis (CTS): The clock tree is created, ensuring that clock signals are routed efficiently across the design, minimizing clock skew.

STA_Setup:

Load Libraries: Load timing libraries which contain the delay information for each cell at different process corners and conditions.

Timing Constraints Definition: Define the timing constraints like clock frequencies, setup and hold times for flip-flops, and required input/output delays.

Pre_Route_STA:

Pre-layout Timing Analysis: STA can be run before the final layout is complete, based on ideal or rough estimates of cell delays and wire delays. This gives an early view of timing violations.

Post_Route_STA:

Detailed Timing Analysis: After placement and routing, STA is run on the final design. This accounts for actual wire delays, parasitic capacitances, and resistances. This is the most accurate timing analysis.

Check Timing Paths: The STA tool checks critical paths to ensure they meet timing constraints (e.g., setup, hold, max delay).

Identify Timing Violations: Paths that violate setup or hold time, or have excessive delay, are flagged as critical violations.

Timing_Optimization:

Slack Calculation: Slack represents the difference between the required and actual signal arrival times. Positive slack means the path meets timing; negative slack indicates a violation.

Fix Violations: Violations are corrected by resizing gates, inserting buffers, or modifying the routing. Retiming or changing placement is also used.

Re-run STA: After making changes, re-run STA to check if the violations are resolved.

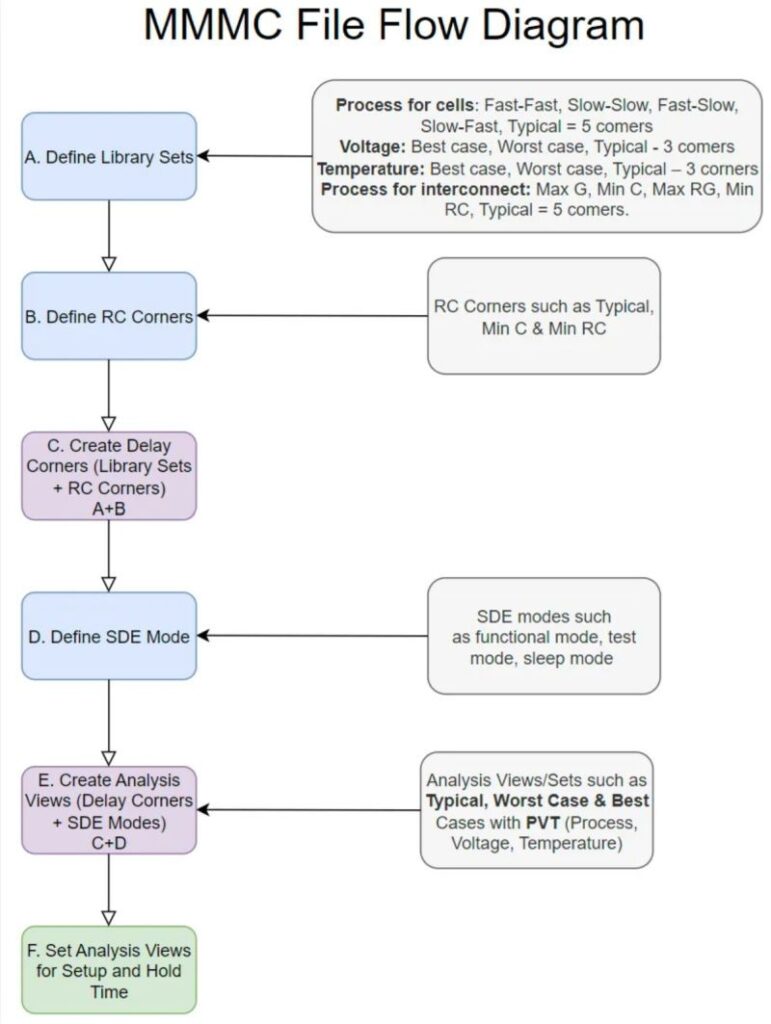

MCMM_Analysis:

Process Corners: Analyze timing for different process corners to account for variations in manufacturing.

Voltage and Temperature (PVT) Corners: Run timing analysis across different voltage and temperature conditions.

Mode-Specific Analysis: Account for different operating modes where timing constraints might vary.

Final_Sign_Off:

STA Sign-Off: Once all timing violations are addressed, perform final sign-off.